4장. 조합 논리

Keyword: Ripple Adder(Half Adder, Full Adder), Carry lookahead Adder, BCD Adder, Decoder, Mux

Decoder, Mux가 제일 중요한 부분인데, 이 때쯤 중간고사 마지막 파트라 필기고 뭐고 디코더, 먹스 그리느라 정신이 없었나보다 ,,ㅎㅎ

1. Full Adder vs Half Adder

2. 리플 가산기 vs 캐리 룩어헤드 가산기 => propagation delay 비교

3. 크기 비교기

4. Decoder

5. Mux

Digital Design With An Introduction to the Verilog HDL, VHDL, and SystemVerilog

1장 ~ 5장 필기. 기록용

'논리 회로' 카테고리의 다른 글

| [논리 회로] Gate-Level Minimization (0) | 2023.11.13 |

|---|---|

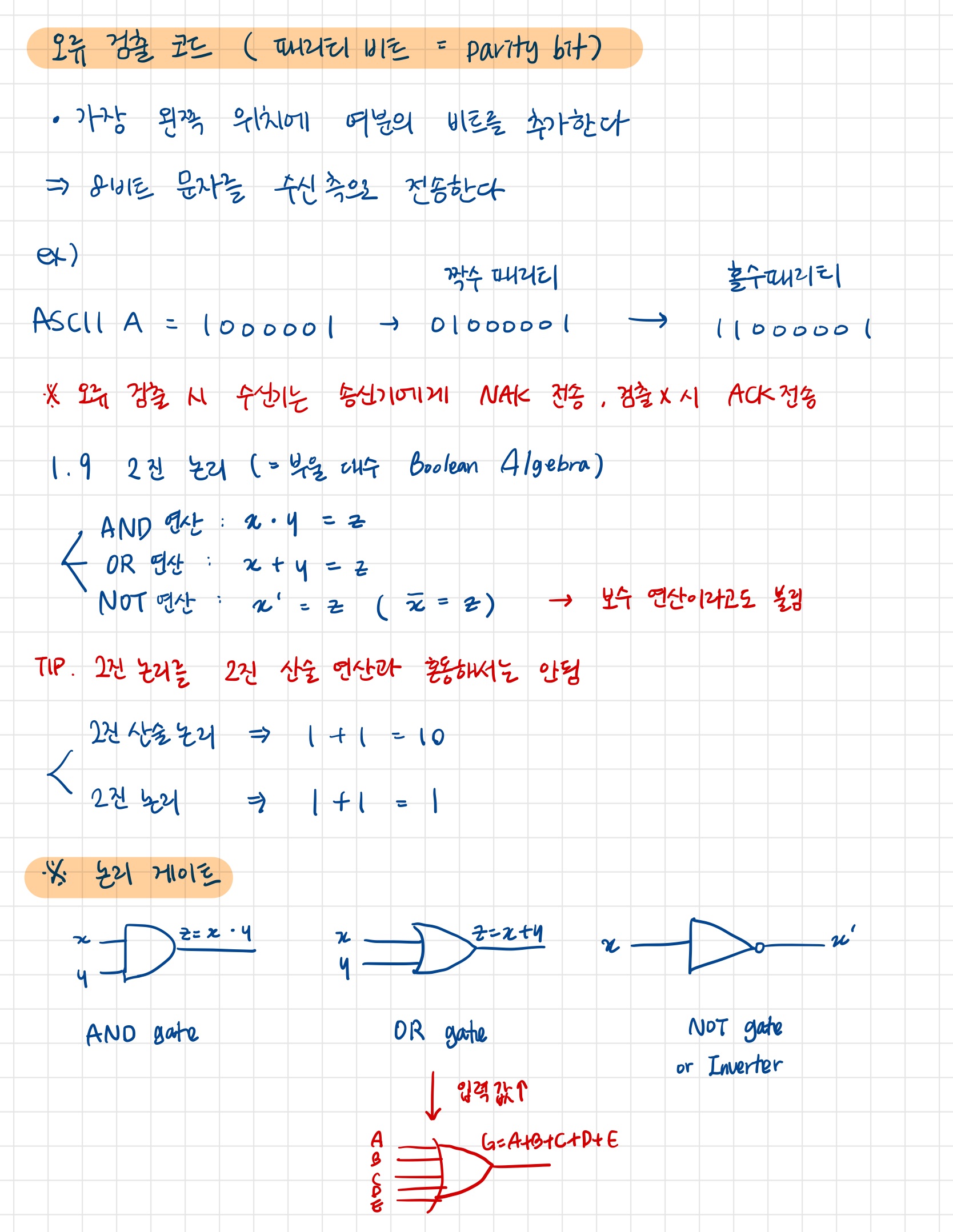

| [논리 회로] Boolean Algebra and Logic gates (0) | 2023.11.13 |

| [논리 회로] Digital System and Binary Numbers (0) | 2023.09.14 |